生成式 AI PCB 設計的(de)下(xià)一個(gè)方向

2023 年,生成式 AI 爆火刷屏,其中大(dà)語言模型 (Large Language Models,LLM) 是毋庸置疑的(de)明(míng)星話(huà)題 —— LLM 似乎已經實現了(le)感知能力,但實際上,LLM 僅擅長(cháng)從曆史和(hé)實時(shí)數據中推理(lǐ)結果。

盡管 “生成式 AI” 近來(lái)才成爲全球熱(rè)詞,但 Cadence 早已将其應用(yòng)到設計流程之中,并稱其爲 “生成式設計”。二者本質相同 —— AI 能夠理(lǐ)解前後節點和(hé)約束條件,像人(rén)類一樣進行推理(lǐ)。

Cadence 客戶已經通(tōng)過我們的(de) Joint Enterprise Data and AI (JedAI) Platform 體會到了(le)生成式 AI 所帶來(lái)的(de)切實好處。芯片設計者也(yě)在使用(yòng) Cadence Cerebrus AI 來(lái)設計更快(kuài)、更便宜、更高(gāo)性能的(de)芯片。

現在, Cadence 将這(zhè)種生成式 AI 技術擴展到了(le)手動布局布線領域。

( 中文字幕 / 英文配音(yīn) )

溫馨提醒:觀看前可(kě)在視頻(pín)下(xià)方設定圖示調整畫(huà)質至 1080p HD,以獲得(de)最佳觀看體驗

AI PCB 設計大(dà)有可(kě)爲

PCB layout 工具首次問世時(shí),它們在布線方面的(de)效果并沒有比手動操作好太多(duō)。如今,規則驅動自動化(huà)縮短了(le)完成特定設計任務所需的(de)時(shí)間,但 PCB 布局布線仍依賴人(rén)工設計,工程師需要考慮信号完整性、電源層、熱(rè)管理(lǐ)等因素。

随著(zhe)多(duō)層設計、3D 堆疊和(hé)異構集成主流化(huà),PCB 布局布線過程變得(de)更加複雜(zá)。設計人(rén)員(yuán)不得(de)不平衡設計的(de)各個(gè)方面,通(tōng)過增加更多(duō) PCB 層數,或降低質量标準,來(lái)避免延誤上市時(shí)間。

在執行計算(suàn)密集型設計任務時(shí),AI 的(de)表現出色過人(rén)。面對(duì)當下(xià)和(hé)未來(lái)日益複雜(zá)的(de) PCB 設計,生成式 AI 提供了(le)引人(rén)矚目的(de)解決方案,這(zhè)正是 Cadence Allegro X AI 産品将其作爲核心功能的(de)原因,該産品已于今年四月(yuè)發布,詳情請閱讀《 Cadence 推出 Allegro X AI,以縮短超過 10 倍的(de)布局布線時(shí)間加速 PCB 設計》。

Allegro X AI 重塑 PCB 設計流程

生成式 AI 在 PCB 設計中最突出的(de)優勢在于,它能夠探索廣闊的(de)設計空間并快(kuài)速高(gāo)效地發現替代解決方案,這(zhè)種能力無人(rén)能及。

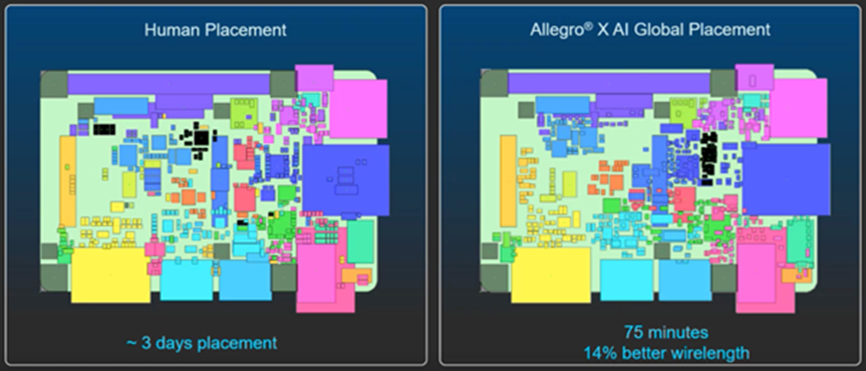

但這(zhè)并非意味著(zhe)在無限的(de)時(shí)間和(hé)資源下(xià),人(rén)類無法達到相同的(de)水(shuǐ)平。生成式 AI 并不比人(rén)類更聰明(míng),但它速度更快(kuài),有助于我們從激烈競争中勝出,讓産品及時(shí)上市。

Allegro X AI 颠覆了(le) PCB 的(de)設計流程。相比于在工程師面前擺出一張空白畫(huà)布,Allegro X AI 會根據最終結果所要求的(de)器件和(hé)規則條件列表,篩選出大(dà)量可(kě)行的(de)設計方案,包括各種布局和(hé)布線選項。對(duì)于專注于設計空間探索 (Design Space Exploration, DSE) 的(de)硬件工程師來(lái)說,這(zhè)項功能非常強大(dà)。雖然這(zhè)在集成電路設計中早已司空見慣,但如今對(duì)于 PCB 設計而言卻至關重要,因爲 PCB 中的(de)集成電路越來(lái)越複雜(zá)。

隻要向生成式 AI 發出指令,它就能根據額外的(de)條件重新生成輸出,這(zhè)在 PCB 設計中也(yě)不例外。設計人(rén)員(yuán)可(kě)以調整約束條件,查看 Allegro X AI 在 8 層内而非 10 層内生成的(de)可(kě)行設計方案,因爲 8 層的(de)設計方案将大(dà)大(dà)節省成本,畢竟每多(duō)一層,整個(gè)電路闆的(de)成本就會多(duō) 10%。

大(dà)規模設計的(de)多(duō)種方案嘗試可(kě)以幫助設計者,在滿足信号完整性、電源設計、熱(rè)管理(lǐ)等需求的(de)情況下(xià),采取最優布線方案。同時(shí),設計周期可(kě)從從數天縮短至數小時(shí),甚至數分(fēn)鐘(zhōng)。更快(kuài)的(de)設計叠代意味著(zhe)更快(kuài)的(de)原型開發和(hé)産品開發,工廠每年可(kě)以制造出更多(duō)的(de)電路闆,并縮短終端産品的(de)上市時(shí)間。

規則不容破壞

PCB 和(hé) IC 設計的(de)另一個(gè)基本差異在于設計的(de)創造性。在 IC 中,設計人(rén)員(yuán)依然在很大(dà)程度上局限于曼哈頓布線策略。但 PCB 存在更大(dà)的(de)自由設計空間,這(zhè)是傳統算(suàn)法無法做(zuò)到的(de),除非大(dà)幅度犧牲設計質量和(hé)線長(cháng)。在這(zhè)一環節,人(rén)類的(de)創造力必不可(kě)少,但代價則是要花費數天反複進行布局試驗。

值得(de)聲明(míng)的(de)是,Cadence 并不是要用(yòng) AI 取代傳統的(de)計算(suàn)算(suàn)法和(hé)自動化(huà)方法。Cadence 始終堅持一流的(de)精準度和(hé) “自動建構校正”。Allegro X AI 的(de)訓練數據十分(fēn)廣泛,其中的(de)設計有成有敗。這(zhè)些數據并不用(yòng)于确定準确與否。

Cadence 将基于物(wù)理(lǐ)的(de)設計算(suàn)法與生成式 AI 相結合,将其用(yòng)作啓發式算(suàn)法,确保輸出的(de)數據準确無誤,同時(shí)也(yě)會借鑒過去積累的(de)集體智慧,實現傳統算(suàn)法無法企及的(de)最佳布局布線。

生成式 AI 能夠很好地模仿人(rén)類的(de)創造力。二者相得(de)益彰,有助于設計人(rén)員(yuán)交付更優秀、更具競争力的(de)産品,并大(dà)幅縮短上市時(shí)間。生成式 AI 讓 Cadence 産品如虎添翼,通(tōng)過更多(duō)解決方案可(kě)能,助力設計“一版成功”。

在下(xià)方視頻(pín)中, Cadence 副總裁 Michael Jackson 討(tǎo)論了(le)如何利用(yòng)基于人(rén)工智能的(de)系統設計技術應對(duì) PCB 布局自動化(huà)的(de)挑戰。Allegro X AI 将傳統的(de)物(wù)理(lǐ)設計算(suàn)法與人(rén)工智能技術相結合,以生成引人(rén)注目的(de) PCB 布局。

歡迎點擊了(le)解 Allegro X AI 亮點 ↓↓↓

( 中文字幕 / 英文配音(yīn) )

溫馨提醒:觀看前可(kě)在視頻下(xià)方設定圖示調整畫(huà)質至 1080p HD,以獲得(de)最佳觀看體驗

Cadence Allegro X AI 技術集成在近日發布的(de) Allegro X Design Platform 23.1 最新版本中!

Allegro X Design Platform 爲 PCB 和(hé)系統設計的(de)工程師提供集成了(le)邏輯 / 物(wù)理(lǐ)設計、系統分(fēn)析和(hé)設計數據管理(lǐ)的(de)系統設計平台和(hé)新的(de)技術升級。

全新的(de) EE 控制面闆,可(kě)進行版圖規劃和(hé)輸入分(fēn)析;集成的(de) X AI 技術,能自動完成元件放置、電源網絡分(fēn)配和(hé)布線;升級更新的(de) Allegro System Capture、Allegro Pulse 數據管理(lǐ)和(hé)雲連接等主要産品,能确保您獲得(de)迄今爲止最強大(dà)的(de) Allegro 性能,将整體設計生産力提高(gāo) 4 倍。

譯文授權轉載出處 (Graser 協同校閱)

長(cháng)按識别 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」