By Paul McLellan, Cadence

在今年舉辦的(de)全球半導體設計大(dà)會 DesignCon 2022 上,來自微軟的(de) Kyle Chen 和(hé) Cadence 的(de) Suomin Cui 聯合發表了(le)《應用(yòng)深度學習和(hé) 3D 電磁求解器實現高(gāo)速靈活互連的(de)優化(huà)設計》技術演講。Kyle 是微軟的(de)混合實境 (MR) 設備訊號完整性 / 電源完整性工程師,Suomin 是 Cadence 的(de)高(gāo)級軟體架構師。演講中所指的(de)「3D 電磁求解器」是 Cadence Clarity 3D Solver,「深度學習」則是在 Optimality Intelligent System Explorer 的(de)早期版本中實現的(de);由於該演講是在 Optimality Explorer 正式發佈之前進行的(de),所以在演講中沒有提到具體的(de)產品名稱。

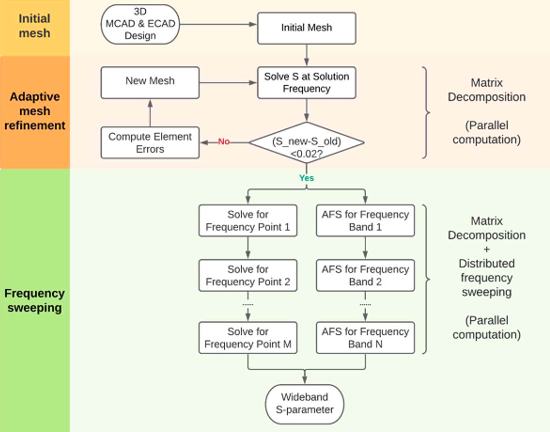

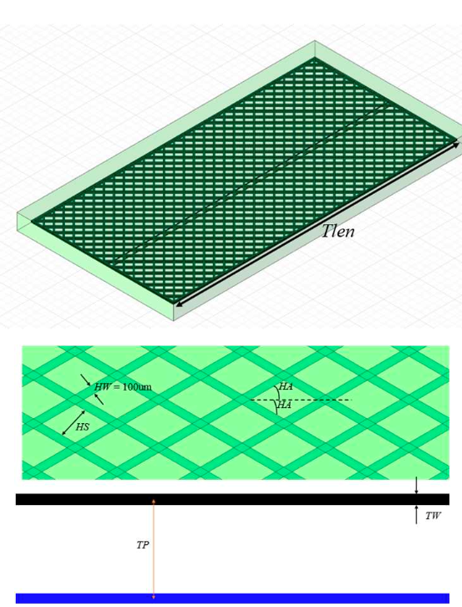

上圖介紹了(le)電磁求解器的(de)工作原理(lǐ)。基本上,首先將設計劃分(fēn)為網格,然後使用(yòng)麥克斯韋方程對許多(duō)不同的(de)頻率進行掃頻。

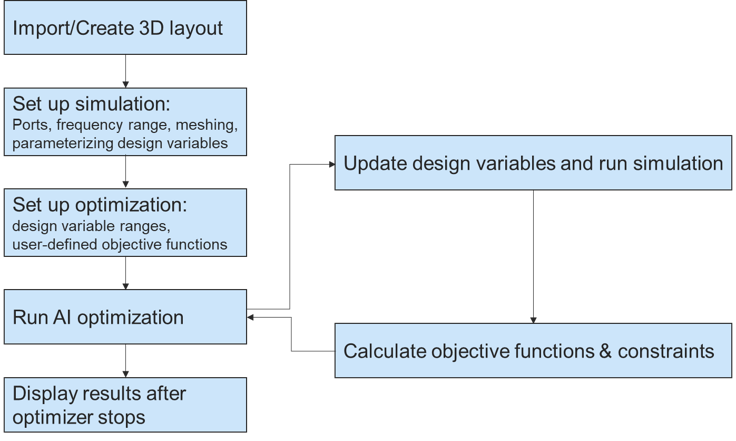

如果採用(yòng)手動的(de)方式,需要設計專家根據自己的(de)專業知識來調整一些變數,然後重新運行 Clarity 3D Solver,查看這些變化(huà)是否發揮了(le)作用(yòng)。而該演講中描述的(de)方法則使用(yòng)了(le)人(rén)工智慧 (AI) 來進行自動調整。設計師設定要優化(huà)的(de)變數,以及範圍和(hé)約束條件,然後定義一個或多(duō)個目標函數。

然後,自動化(huà)過程將根據設定的(de)範圍和(hé)約束條件改變變數,使目標函數最小化(huà),如上圖所示。Kyle 更深入地研究了(le)優化(huà)的(de)工作原理(lǐ)。當斯蒂芬·霍金撰寫《時間簡史》時,有人(rén)告訴他(tā),在書中每寫一個方程式,都將使銷量減半;因此本文將不對積分(fēn)符號和(hé)矩陣代數提供詳細的(de)解釋。

堆疊微孔

多(duō)層軟硬結合印刷電路闆 (rigid-flex printed circuit ,即 RFPC) 在軟性區使用(yòng)帶狀佈線。由於彎曲要求,高(gāo)速佈線需要具有較薄的(de)材料層和(hé)填充接地平面。高(gāo)密互連 (high-density interconnector ,即 HDI) PCB 涉及盲孔、埋孔和(hé)堆疊微孔。

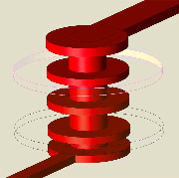

堆疊微孔需要在所有過渡層上使用(yòng)非功能性焊盤,藉由順序層壓和(hé)鐳射鑽孔來創建。最初的(de)設計使用(yòng)統一的(de)過孔焊盤尺寸 (如上圖),但都是透過以下(xià)參數得(de)出的(de):

|

第 x 層上的(de)焊盤尺寸的(de)半徑 |

|---|---|

|

過孔管的(de)半徑 |

|

第 x 層上的(de)反焊盤尺寸的(de)半徑 |

|

埠 y 處的(de)走線寬度 |

|

約束條件:過孔參數不是獨立的(de),並且受到許多(duō)製造方面的(de)限制,如長寬比 |

|

為了(le)簡化(huà)起見 (之後會更改),使用(yòng)整片接地平面來優化(huà)過孔 |

然後用(yòng)這些參數進行人(rén)工智慧優化(huà),以便使回波損耗降至最低。第一次運行在回波損耗達到 -35dB 時停止 (85-88 次試驗時也(yě)是如此)。第二次運行在 250 次試驗時停止,在 100 次運行內實現了(le)約為 -40dB 的(de)回波損耗,然後開始偏離 (原因尚不清楚)。

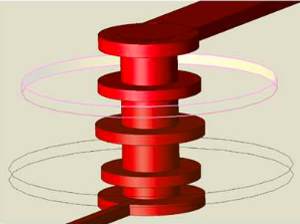

如果提供更多(duō)的(de)參數進行優化(huà),可(kě)以得(de)到更好的(de)結果。最終的(de)結果詳見下(xià)圖,其中過孔焊盤的(de)尺寸不再統一。經過 100 次試驗,回波損耗低於 -40dB。獲得(de)最佳結果使用(yòng)了(le) 375 個試驗樣本,回波損耗為 -42.5dB。

參數化(huà)的(de) FPC 差分(fēn)對

下(xià)一個優化(huà)項目是軟性印刷電路 (flexible printed circuit ,即 FPC) 差分(fēn)對,同時優化(huà)傳輸線、接地網格和(hé)介電質厚度。

同樣,在這種情況下(xià),也(yě)像過孔堆疊一樣進行參數化(huà):

|

填充寬度 |

|---|---|

|

填充間距 |

|

填充角 |

|

傳輸走線寬度 |

|

傳輸線走線間距 |

|

介電質厚度 |

最終找到了(le)多(duō)種有效的(de)解決方案。研究發現,人(rén)工智慧在尋找接地網格圖案的(de)對稱性時頗為艱難,但添加對稱性約束並迫使網格圖案呈 45° 角就可(kě)以更輕鬆地完成。然後在 100 個試驗樣本內實現了(le)低於 -30dB 的(de)回波損耗。

設計總結

微軟對此次設計探索和(hé)技術演講的(de)總結如下(xià):

|

此次探索的(de)優化(huà)方法適用(yòng)於過孔結構和(hé)傳輸線的(de)軟硬結合 PCB 設計 |

|---|---|

|

此次探索提出了(le)一種相關性,可(kě)證明(míng) 3D 模型的(de)準確性,該模型採用(yòng)了(le) Clarity 3D Solver 進行模擬的(de)結果和(hé)測量值對比 |

|

然後根據相關的(de) FPC 疊層和(hé)材料資料進行優化(huà) |

|

此次探索展示了(le)機器學習之間的(de)互動和(hé)相互學習,以及從機器中學習,這可(kě)能會產生新的(de)設計方法 |

|

在進行了(le)幾次優化(huà)後,瞭解了(le)優化(huà)趨勢,並制定了(le)新的(de)有效設計規則,實現了(le)對 RFPC 差分(fēn)對的(de)設計目標。 |

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」