現代電腦系統的(de)許多(duō)介面都採用(yòng)了(le)雙倍資料速率 (DDR) 技術,其中之一涉及到處理(lǐ)器與記憶體的(de)工作方式,人(rén)工智能 (AI) 、機器學習 (ML) 和(hé)資料挖掘等新應用(yòng)也(yě)在不斷推動這種介面突破新的(de)極限。

針對高(gāo)頻寬同步動態隨機存取記憶體 (SDRAM) 的(de)最新 DDR5 版本 DDR 介面的(de)開發始於 2017 年,而備受期待的(de) JESD79-5 DDR5 SDRAM 標準於 2020 年 7 月(yuè)發布。

借助 Cadence® Sigrity™ X 進行兼顧電源影(yǐng)響的(de)訊號完整性 (SI) 分(fēn)析,並將其作為 DDR5 應用(yòng)設計和(hé)驗證流程的(de)一部分(fēn),工程師可(kě)以確信最終產品將與規格相符,並實現更好的(de)性能。

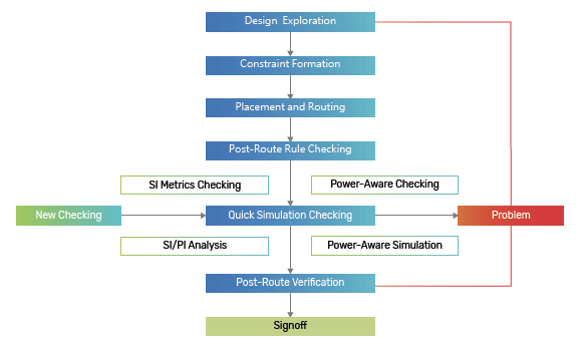

兼顧電源影(yǐng)響的(de)約束驅動的(de)流程

本書為 PDF 版本,共 7 頁,將細說 DDR5 技術,以及使用(yòng) Cadence Sigrity X 對 DDR5 設計進行兼顧電源影(yǐng)響的(de)訊號完整性分(fēn)析的(de)優勢和(hé)關鍵要點,以減少叠代,確保所需的(de)簽核級準確度,符合 DDR5 規範。

本書重點

|

設計概述 |

|---|---|

|

DDR5 的(de)優勢 |

|

設計挑戰:電源完整性和(hé)訊號完整性 |

|

兼顧電源影(yǐng)響的(de) DDR5 訊號完整性分(fēn)析 |

|

FDTD 方法 |

|

簽核模擬 |

|

結論 |

中文版授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」