By Team Sigrity, Cadence

判斷您的(de)設計是否能耐受 ESD 事件的(de)方式是用(yòng) ESD 槍在實驗室裡測試一遍。結果或許可(kě)行,或許不行。如果不行,另外尋求一個提高(gāo)性能的(de)設計方案將是很花費時間和(hé)成本的(de)。就算(suàn)結果可(kě)行,那您能保證不會再加上更多(duō)的(de) TVS 二極體作為保護嗎?您的(de)競爭對手也(yě)許擁有一套更便宜的(de)設計並且性能和(hé)您的(de)一樣。因此,實驗室測試是一種方法,但不是完美(měi)的(de)。

在搭建設計之前模擬ESD事件會更為有效。如果模擬通(tōng)過了(le),您就可(kě)以針對成本進行優化(huà)了(le)。如果沒通(tōng)過,您可(kě)以調整您的(de)設計方案而不用(yòng)設計一個新的(de) PCB。模擬讓您的(de)設計變得(de)既省時又省錢。

OK,就這麼定了(le),那我們開始吧。但是真的(de)有這麼一套工具可(kě)以模擬 ESD 事件並且有利於更好的(de)設計嗎?如果您稍微搜索一下(xià),可(kě)能得(de)不到什(shén)麼結果。一個值得(de)信賴的(de) ESD 模擬需要一些相當先進的(de)場求解和(hé)路求解器。一些工具供應商或許提供了(le)一些 ESD 保護的(de)設計指南(nán),但真的(de)很難找到一種在實際的(de)硬體生產和(hé)測試之前能夠可(kě)靠地預測 ESD 對系統影(yǐng)響的(de)工具。

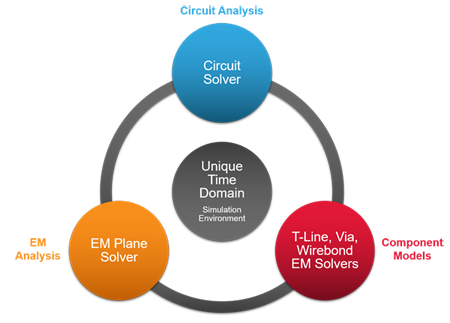

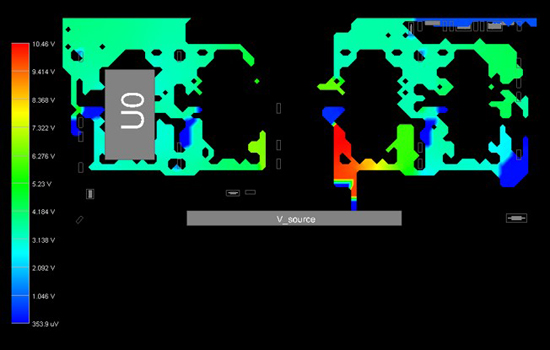

圖1:Sigrity SPEED2000™ 技術可(kě)提供可(kě)靠的(de) ESD 模擬

因此,ESD 到底是什(shén)麼?一陣突如其來的(de)電流是怎樣給物(wù)體充電發生 ESD 事件的(de)?當帶有電荷的(de)人(rén)觸碰到行動電話,或者用(yòng)帶電的(de)電纜插入 USB 埠時,ESD 事件就會發生。

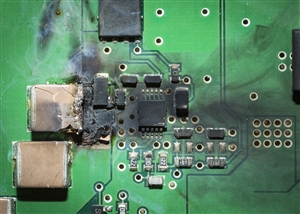

ESD 放電將導緻幾千伏的(de)電壓,並產生幾安培的(de)電流,這對一個電子器件或者電子系統來講會造成嚴重的(de)破壞。如果高(gāo)速電路系統遭受 ESD 事件衝擊,將導緻幾個時間週期的(de)信號不正常。例如,您的(de)行動電話可(kě)能斷線,或者您的(de)筆記型電腦可(kě)能出現運行錯誤。

因此,問題是嚴重的(de),模擬聽上去是一個好主意。如果您現在還沒有對 ESD 進行模擬過,您將來想要進行 ESD 模擬時如何選擇模擬工具呢(ne)?為了(le)模擬 ESD 的(de)影(yǐng)響,模擬工具必須滿足怎樣的(de)條件才可(kě)幫助設計工程師瞭解在實驗室中設計在 ESD 激勵下(xià)如何運作?

因為 ESD 是一種具有非常高(gāo)電壓的(de)瞬態現象,並且會導緻大(dà)量的(de)不需要的(de)電流流過系統的(de)任意部分(fēn),這個模擬工具就需要一個帶有場求解器時域的(de)模擬器去類比任何導體的(de)形狀/路線;它也(yě)需要能處理(lǐ)非線性器件以便於分(fēn)析信號及優化(huà) ESD 保護,例如 TVS 二極體。當所有這些條件滿足後,ESD 模擬功能實際上已經可(kě)以被當作能進行標準 ESD 測試的(de)虛擬的(de)實驗室了(le),並且給出能足以被您信任的(de)模擬結果。

Sigrity SPEED2000 技術經得(de)起 ESD 模擬的(de)挑戰,並且為虛擬環境提供了(le)一整套工作流程。目標是說明(míng)設計工程師獲得(de)在沒有超標準的(de) ESD 保護設計下(xià)不會測試失敗的(de)高(gāo)速系統設計。

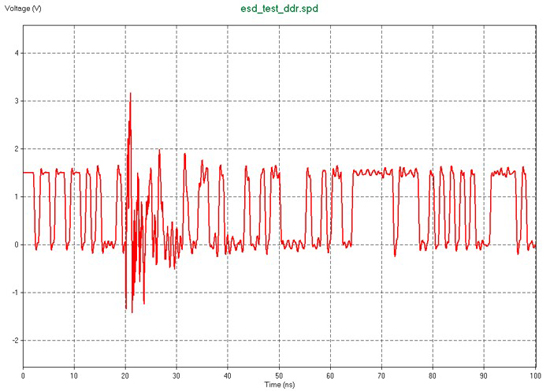

ESD 工作流程利用(yòng)獨有的(de)混合時域模擬器模擬 ESD 槍電路以及實際的(de)系統結構戰,利用(yòng)一個預配置的(de)ESD槍模型滿足 IEC61000-4-2 的(de)實驗室測試標準戰,工程師就可(kě)以模擬 ESD 事件了(le)。將這個槍模型放置于一個 PCB/封裝版圖的(de)任意位置,就可(kě)以模仿真實的(de) ESD 槍激勵真實的(de) PCB 時所發生的(de)現象。這個槍模型產生激勵系統的(de)標準電壓電流,同時所有的(de)導體也(yě)被模擬進去了(le)。該工具透過電流在一個實際測試環境中流過的(de)路徑捕獲 ESD 電流,並且在器件的(de)引腳測量這個高(gāo)電壓,這樣就可(kě)以告訴工程師闆上的(de) IC 器件是否能經受住 ESD 的(de)影(yǐng)響。工程師就可(kě)以決定是否需要加更多(duō)的(de)保護,或者多(duō)餘的(de)保護是否需要被移除以降低成本。

這裡有一個給設計工程師的(de)小技巧:不要僅僅依靠通(tōng)過加 TVS 器件來對您的(de) PCB 進行 ESD 保護。其他(tā)的(de) PCB 器件,例如去耦電容以及衰減電阻,也(yě)能提供一定程度的(de)保護。採用(yòng) SPEED2000 的(de)工作流程,我們可(kě)以很容易地檢查出這些器件對 ESD 保護的(de)貢獻,因此,可(kě)以減小 TVS 器件的(de)使用(yòng)。

當您模擬完您的(de) PCB 後,我們非常希望得(de)到您的(de)回饋以確認它是否符合 ESD 測試的(de)需求。

相關技術應用(yòng)影(yǐng)片

|

|---|

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」