By Paul McLellan

如今,各式各樣的(de) 3D 封裝呈增長趨勢,但還未引起廣泛關注。在 2019 年夏季的(de) HOT CHIPS 上,大(dà)部分(fēn)設計並未採用(yòng)單個大(dà)裸晶 (Die),而是採用(yòng)同一封裝中的(de)多(duō)裸晶設計方法。

我們可(kě)以對「摩爾定律的(de)終結」究竟意味著什(shén)麼展開探討,但是顯然,不再有令人(rén)信服的(de)經濟理(lǐ)由將設計應用(yòng)在 7 奈米 (及以下(xià)) 的(de)工藝中。如果我們的(de)需求是性能更高(gāo)、或功率更低、或密度更低,那怎麼辦呢(ne)?直到最近,在設計中應用(yòng)最尖端的(de)工藝還能不僅實現上述需求,更能使每個電晶體的(de)成本更低。也(yě)就是說,即使我們的(de)設計是在前一代節點中執行的(de),也(yě)有經濟上的(de)理(lǐ)由來保持領先。競爭環境也(yě)是推動因素 —— 如果我們不選擇轉移到先進節點,而競爭對手卻進行了(le)轉移,那麼我們勢必會在成本耗費上處於巨大(dà)劣勢。在過去的(de)幾年甚至幾十年中,制程節點的(de)經驗法則表明(míng):如果電晶體密度倍增,相比於之前的(de)節點,每平方毫米的(de)成本僅高(gāo)出 15%;因此,成本節約了(le) 35%。不過這種說法現在已不再成立,正如上方圖表所示,該圖表出自 Lisa Su 在 HOT CHIPS 上的(de)主題演講。

另一個趨勢是 3D 封裝價格越來越低廉,因為不少設計都投入了(le)大(dà)批量生產,其中尤以智慧手機和(hé)伺服器為多(duō)。正因成本平衡產生變化(huà),如今,將所有專案整合到一個大(dà)型系統級晶片 (SoC) 上的(de)方法不再像之前那樣吸引人(rén);相比之下(xià),將多(duō)裸晶整合到一個封裝更能引人(rén)矚目。儘管如何決策受設計的(de)詳情和(hé)實際成本的(de)影(yǐng)響,但未來趨勢方向是明(míng)確的(de) ——「超越摩爾」廣為人(rén)知,正逐漸取代「摩爾定律」的(de)地位。

另一個製造現狀顯示,相比於分(fēn)成獨立裸晶的(de)相同設計,超大(dà)型晶片的(de)良率更低。如果設計採用(yòng)一個大(dà)型多(duō)核處理(lǐ)器或 FPGA,由於二者裸晶相同,故將設計分(fēn)成多(duō)裸晶的(de)方式更為可(kě)行。在所有設計的(de)最高(gāo)端領域,有一項硬性限制,即最大(dà)標線尺寸,也(yě)就是製造設備可(kě)以處理(lǐ)的(de)最大(dà)設計。如果某項設計超過最大(dà)設計,則隻能選擇將其分(fēn)成多(duō)裸晶,除此之外,別無他(tā)法;也(yě)許,可(kě)以將其單獨封裝成「晶片組」,但更多(duō)採用(yòng)的(de)是 3D 封裝形式。

純數位之外的(de)設計元件,例如類比、射頻、光(guāng)子或高(gāo)速 SerDes I/O 等,壓根無法從等比例縮小中得(de)到任何好處。之所以將設計的(de)此類元件在舊節點中保留,還有一個原因在於新節點早期上市時間,設計的(de)此類元件需要測試晶片和(hé)矽工藝的(de)驗證。如將其在舊節點中保留,這些測試晶片會脫離新節點中第一個設計的(de)關鍵路徑。

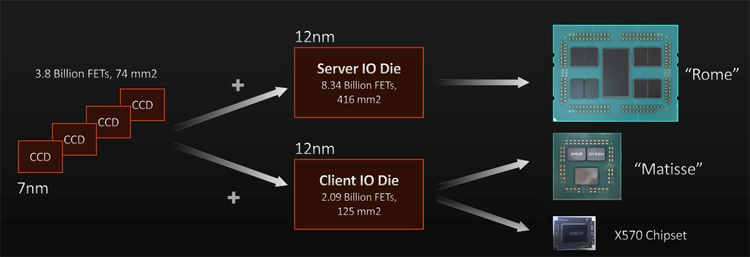

舉例說明(míng):在 HOT CHIPS 上展示過的(de) AMD 的(de) Zen2。同一封裝中,AMD 的(de) Zen2 具有幾個相同的(de)計算(suàn)晶片和(hé)一個用(yòng)戶端或伺服器 I/O 晶片。計算(suàn)晶片內置 7 奈米,配備 3.8B 電晶體。伺服器和(hé)用(yòng)戶端 I/O 晶片均內置 12 奈米。相比於配備 2B 電晶體的(de)用(yòng)戶端晶片,配備 8.3B 電晶體的(de)伺服器晶片要大(dà)得(de)多(duō)。在同一個仲介層上,AMD 的(de) Rome 伺服器產品配備八個計算(suàn)晶片和(hé)伺服器 I/O 晶片。Matisse 用(yòng)戶端版本配備兩個計算(suàn)晶片和(hé)用(yòng)戶端 I/O 晶片。查看上圖詳見展示。

HOT CHIPS 上展示的(de)其他(tā)幾個設計方案也(yě)與之相似,即將純數位計算(suàn)引擎設置進一個先進的(de)節點,並在一個先進節點上製作第二個晶片來容納 SerDes、射頻、類比、光(guāng)子等設計需要的(de)專案。

Chiplets 小型裸晶

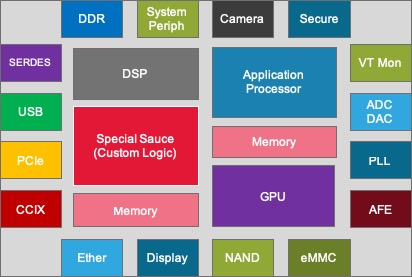

一旦人(rén)們接受並非所有專案都需要在同一個制程節點中進行設計這一觀點,則長遠來看,採用(yòng)更模組化(huà)的(de) SoC 方案可(kě)能會更具吸引力,因為相對而言,會有較多(duō)小型裸晶,即 chiplets。

Chiplet 價值定位在於:

|

靈活選擇元件的(de)最佳制程節點。尤其是,SerDes I/O 和(hé)模擬無需設置在「核心」制程節點中。 |

|---|---|

|

裸晶尺寸小,良率更高(gāo) |

|

使用(yòng)預先存在的(de) chiplets,縮短積體電路設計週期和(hé)整合複雜度 |

|

透過購買已知良好裸晶 (KGD),來降低製造成本 |

|

如在多(duō)個設計中使用(yòng)同樣的(de) chiplets,則批量製造具有成本優勢 |

此法的(de)長期願景是,系統級封裝 (SiP) 成為新的(de) SoC,而 chiplets 成為新的(de)「IP」。然而,chiplets 之間需要配備標準 / 通(tōng)用(yòng)的(de)通(tōng)信介面,才能實現這一願景。

這個基本思路並非現在才被提出。事實上,戈登·摩爾 (Gordon Moore) 在其 1965 年的(de)電子文章(zhāng)中就對後人(rén)熟知的(de)摩爾定律進行了(le)介紹,文中,他(tā)還表明(míng):

「用(yòng)較小的(de)功能構建大(dà)型系統可(kě)能會更為經濟,這些功能是分(fēn)開封裝和(hé)互連的(de)。」

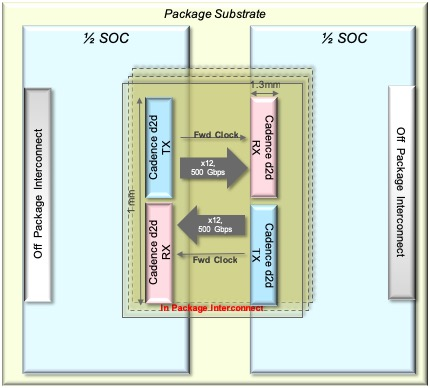

Die-to-Die (D2D,裸晶對裸晶) 互連

Cadence 公司已創建了(le)一個 7 奈米 UltraLink D2D PHY IP 和(hé)一個測試晶片 (即測試 chiplet),包含用(yòng)於晶片對晶片連接的(de) 40G SerDes,以及裸晶對裸晶 (D2D) 的(de)高(gāo)頻寬、低功耗、低延遲封裝內互連。其功耗低、NRZ (與 PAM-4 相比),且不具有前向改錯碼 (FEC)。頂層設計的(de)目標是將裸晶邊緣 (beachfront) 的(de)頻寬提升至最大(dà),避免 bump 間距過小,從而避免使用(yòng)昂貴的(de)矽基闆 (不過,如有其他(tā)原因,例如使用(yòng) HBM 記憶體堆疊驅動,則可(kě)以使用(yòng)這些矽基闆)。

詳情如下(xià):

|

線路速率為 20-40Gbps |

|---|---|

|

~500Gbps 雙向頻寬,1 毫米 beachfront |

|

@奈奎斯特 (25-40 毫米) 插入損耗為 8 db |

|

超低功耗 ~ 1.5pj/bit |

|

超低延遲 (~2.8ns TX,~2.6ns RX) |

|

直流耦合 |

|

前向時鐘原始比特誤碼率 1e-15,無前向改錯碼 |

|

單端 NRZ 信令,配備用(yòng)於信號完整性和(hé)電源完整性的(de)空間編碼 |

|

鏈路管理(lǐ)頻帶 |

|

MCM 應用(yòng)的(de)目標 bump 間距 (130u) |

|

支持矽仲介層的(de)微型 bump |

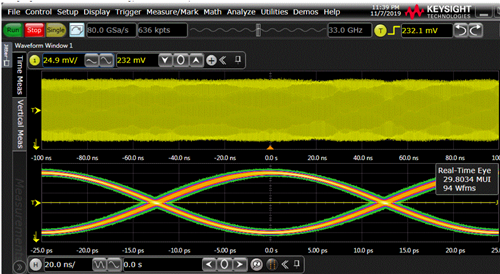

40G PHY 眼圖如下(xià)所示:

範例設計

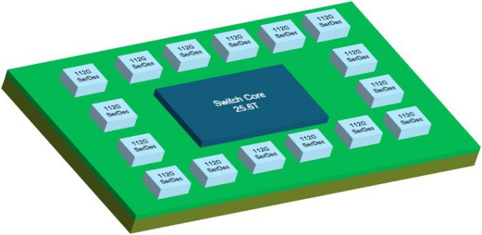

有關此技術支持的(de)一種設計示例,詳見上圖所示的(de) 25.6Tbps 交換機設計。其建立在有機基闆上 (價格比仲介層更低);每個 chiplet 提供 1.2 Tbps 的(de)頻寬,因此,其中 16 個 chiplets 的(de)總頻寬為 25.6 Tbps。D2D 介面位於 chiplets 和(hé)交換機核心本身之間。

SEMI

與此同時,SEMI 發佈了(le) 2019 年異構整合線路圖,概述和(hé)執行摘要可(kě)複製連結並訪問:http://suo.im/6igEtr

譯文授權轉載出處

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」