By Jiefu Wu, Graser

【 PCB 設計同步分(fēn)析 】系列專題將解密六大(dà)隱藏分(fēn)析技巧,幫助 EE、Layout 人(rén)員在設計前期階段不需依靠 SI / PI 專家就能做(zuò)初步的(de)模擬分(fēn)析,快(kuài)速找出並排除常見訊號 / 電源問題,提升設計品質和(hé)效率。接下(xià)來會帶領大(dà)家一一解鎖 IR Drop、Coupling、Impedance、Crosstalk、Reflection、Return Path 分(fēn)析技巧,歡迎共同探討。

一個理(lǐ)想的(de)電源供應環境,對電子產品的(de)運作至關重要;而如何提供良好的(de)電源供應,除了(le)在硬體設計時規劃足夠的(de)電源功率以供應負載,在 PCB 設計時針對電源傳輸路徑進行分(fēn)析最佳化(huà),避免 IR Drop 產生,亦是必要的(de)過程。

本系列首篇將與大(dà)家分(fēn)享如何使用(yòng) Allegro 的(de) IR Drop 分(fēn)析功能,在 PCB 設計過程中快(kuài)速進行壓降分(fēn)析,幫助 PCB 設計團隊即時排除常見電源問題,最佳化(huà)電源供應設計。

什(shén)麼是 IR Drop?

在開始之前我們先來說說什(shén)麼是 IR Drop。想像一下(xià):將一張 PCB 化(huà)作人(rén)體的(de)血液循環系統,PCB電源供應的(de)源頭好比是心臟,PCB 上的(de)各種零件是不同的(de)器官,而電源供應的(de)路徑就是血管。

當血液從心臟流到各個器官時,如果某部分(fēn)的(de)血管壁阻塞,便會造成嚴重的(de)疾病。若發生問題的(de)部位是在腦部,就會造成腦部缺血型栓塞,也(yě)就是我們說的(de)腦中風;同樣的(de)情況拿到 PCB 上來說,如果電源導通(tōng)路徑過窄,電阻過高(gāo),便會造成電壓衰退 (IR Drop),使元件動作不正常。

Vdrop = I * R

為什(shén)麼需要 IR Drop 分(fēn)析?

一般在設計 PCB 時,IR Drop 常於以下(xià)幾種情況發生:

1. |

電源路徑過長。 |

|---|---|

2. |

電源路徑過窄。 |

3. |

電源鋪銅平面過孔 (VIA) 換層傳輸,但孔徑過小及數量不足。 |

4. |

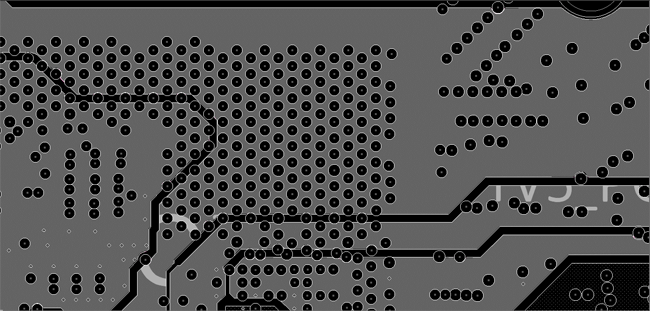

電源鋪銅平面經過它層通(tōng)孔密集區,導緻鋪銅破碎形成瑞士起司效應 (Swiss Cheese)。(圖1) |

圖 1. 瑞士起司效應

以往 PCB 設計團隊在處理(lǐ)電源部分(fēn)時,多(duō)半依據過往經驗或是其他(tā)輔助計算(suàn)工具 (如 Saturn PCB Design) 來評估電源平面鋪銅或是走線過孔是否合理(lǐ)。在大(dà)部分(fēn)的(de)時候,如果你足夠細心,會詳細檢查並修正設計,基本上成果應該不會有太大(dà)問題。但天有不測風雲,人(rén)有旦夕禍福。

PCB 設計團隊要處理(lǐ)面對的(de)問題有千百種,不單單僅是 PCB Layout。有時候雜事一多(duō),你就忽略了(le)本來需要修正的(de)地方;更有時候可(kě)能 PCB 設計人(rén)員的(de)經驗不是那麼足夠,他(tā)認為電源有接上就沒問題了(le)。就執筆者本身的(de)經驗,就常遭遇到如上提及的(de)情況:電源鋪銅平面過孔 (VIA) 換層傳輸,但孔徑過小及數量不足。

在某個案例裡,電源經由平面鋪銅供應到 PCB 中央的(de) BGA 區域,中間先經過一顆電容濾波。鋪銅的(de)寬度足夠,沒問題;電容的(de)選用(yòng)也(yě)很合理(lǐ),零件 Footprint 夠大(dà) (1206),PAD 面積足以應付電流供應。一切都看起來很理(lǐ)想。

但是,問題就是這個: 在每一個電容的(de) PAD 上,隻打了(le) 2 個僅 8mil 孔徑的(de) VIA 孔來做(zuò)導通(tōng)。

悲劇結果就不用(yòng)多(duō)說了(le)。在接下(xià)來的(de)改版當中工程師花費了(le)相當多(duō)的(de)時間去修正零件佈置及針對每一個電容 PAD 增加大(dà)孔徑的(de)導通(tōng)孔。

另一個例子是 PCB 上有多(duō)顆 Power IC 串接,但隻使用(yòng) 10mil 線寬的(de)走線,導緻系列成品在使用(yòng)一段時間後 Power IC 開始產生異常。

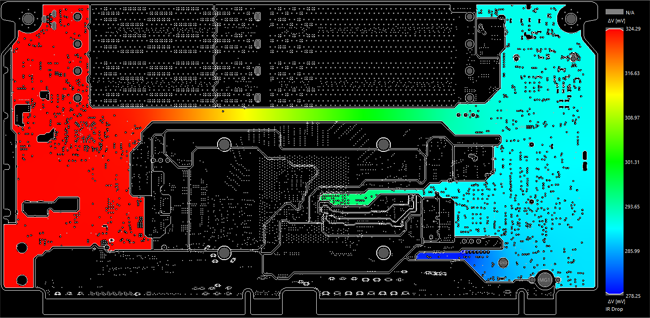

或是下(xià)圖中左右兩片大(dà)平面鋪銅,僅靠一段窄銅面連接,這當中一定有什(shén)麼誤會!

若能在一開始設計 PCB 電源部分(fēn)時,能有一個直觀的(de)輔助分(fēn)析工具幫助工程師即時分(fēn)析、即時檢查、即時修正,將可(kě)大(dà)大(dà)減少設計重複修改的(de)機會。套一句現在流行的(de)話,超前部署,避免心血結晶於最後關頭付之一炬。

如何執行 IR Drop 即時分(fēn)析 PCB 電源設計

現在 Allegro 中導入了(le) Sigrity 專業的(de)模擬分(fēn)析技術,將 IDA (In-Design Analysis, 設計同步分(fēn)析) 帶入 PCB 設計流程之中,幫助 PCB 設計團隊預先且即時的(de)分(fēn)析電源設計,並修正不理(lǐ)想的(de)部分(fēn),使設計效率提升,不良機率減少。下(xià)方影(yǐng)片將帶你快(kuài)速瞭解 Allegro 的(de) IR Drop 分(fēn)析工作流程。

( 中文配音(yīn) ; 建議開啟音(yīn)訊聆聽觀看 )

想進一步了(le)解更多(duō)操作 Tips?

歡迎點擊下(xià)方圖片,下(xià)載 完整「 PCB 設計同步分(fēn)析六大(dà)隱藏技巧 」電子書。

本電子書為 PDF 版本,全文 94 頁,將以實例逐一解鎖6大(dà)分(fēn)析技巧,幫助您在設計前期階段不需依靠 SI / PI 專家就能做(zuò)初步的(de)模擬分(fēn)析,快(kuài)速找出並排除常見信號 / 電源問題,提升設計品質和(hé)效率。

※ 下(xià)一篇文章(zhāng)預告:Coupling 分(fēn)析技巧