By Cadence

本文要點

|

PCB 差動對的(de)基礎知識。 |

|---|---|

|

差動對佈線指南(nán),實現更好的(de)佈線設計。 |

|

高(gāo)效利用(yòng) PCB 設計工具。 |

「眾人(rén)拾柴火焰高(gāo)」 ——資源整合通(tōng)常會帶來更好的(de)結果。畢竟「三個臭皮匠(jiàng),頂個諸葛亮」,在電子領域也(yě)是如此:較之單一的(de)走線,差動對佈線更受青睞。

不過,差動訊號對 (Differential Pair) 佈線可(kě)能沒那麼容易,因為它們必須遵循特定的(de)規則,這樣才能確保訊號的(de)性能。這些規則決定了(le)一些細節,如差動對的(de)走線寬度和(hé)間距,以及許多(duō)其他(tā)方面,如導線如何在電路闆上一起佈線。如果使用(yòng)了(le)大(dà)量的(de)差動對,即使設計師已經為每個訊號佈設了(le)兩條單獨的(de)走線,也(yě)會對電路闆其他(tā)部分(fēn)的(de)佈線產生很大(dà)的(de)影(yǐng)響。本文將詳細介紹差動對的(de)佈線和(hé)一些需要注意的(de)潛在問題。

PCB 差動對的(de)基礎知識

在開始了(le)解差動對佈線的(de)潛在困難和(hé)解決方案之前,先回顧一下(xià)基礎知識。有過 PCB layout 經驗的(de)人(rén)一定熟悉單端訊號。單端訊號是指在一條走線上傳輸訊號,然後使用(yòng)一個共同的(de)參考平面作為訊號的(de)返回路徑。當我們在電路闆上佈線時,接地平面是訊號的(de)返回路徑,這就是單端訊號。大(dà)多(duō)數 PCB 網路都是這樣佈線的(de)。

然而,這種佈線方式有一個問題:隨著傳輸線速度提高(gāo),單端訊號可(kě)能會受到一些問題的(de)影(yǐng)響,包括串擾雜訊和(hé)電磁幹擾 (EMI)。此時,差動訊號就派上了(le)用(yòng)場。

差動訊號使用(yòng)兩個互補的(de)訊號來傳輸一個資料訊號,但第二個訊號與第一個訊號的(de)相位相反。訊號接收器使用(yòng)反相和(hé)同相訊號之間的(de)差異來破譯資訊。使用(yòng)差動對佈線傳輸訊號有一些重要的(de)好處,首先是能減少雜訊和(hé) EMI:

|

傳入的(de)幹擾將被均等地添加到反相和(hé)同相的(de)訊號中。由於接收器是對兩個訊號之間的(de)差異作出反應,無論是否受到影(yǐng)響,影(yǐng)響都是最小的(de)。與影(yǐng)響單端訊號的(de)幹擾相比,這樣的(de)性能要好得(de)多(duō)。 |

|---|---|

|

差動對的(de)電磁場大(dà)小相等,但極性相反,因此來自兩條走線的(de)幹擾通(tōng)常可(kě)以相互抵消。 |

印刷電路闆上的(de)差動對佈線

與單端訊號相比,差動對還有一個優勢,那就是它們可(kě)以在較低的(de)電壓下(xià)工作。單條走線必須在較高(gāo)的(de)電壓下(xià)工作,以確保其信噪比 (SNR) 足以抵禦任何傳入的(de)雜訊。差動對對雜訊的(de)抗幹擾能力更強,因此需要的(de)電壓更低,這提供了(le)一些額外的(de)好處:

|

所需的(de)電壓更低意味著功耗也(yě)更低。 |

|---|---|

|

訊號的(de)電壓轉換將更小,有助於確保電路闆的(de)電源完整性。 |

|

在較低的(de)訊號電壓下(xià)可(kě)以使用(yòng)較高(gāo)的(de)工作頻率。 |

|

電壓越低,輻射的(de) EMI 就越少。 |

如上所述,在電路闆上使用(yòng)差動訊號有諸多(duō)好處,但也(yě)要付出一些代價。

PCB layout 中與差動對相關的(de)問題

如上文所述,使用(yòng)差動對佈線有諸多(duō)好處,但也(yě)有一些缺點。第一個也(yě)是最明(míng)顯的(de)問題是,必須為每個訊號佈設兩條走線。這不僅使電路闆上的(de)佈線量增加了(le)一倍,而且由於差動對有額外的(de)規則,還會佔用(yòng)更多(duō)的(de)空間。我們來看看設計師在進行差動對佈線時不得(de)不面對的(de)一些難題。

差動對中兩條走線的(de)長度必須相等

差動對的(de)一大(dà)優勢是,透過兩個極性相反的(de)均等訊號來代表訊號,可(kě)以 消除雜訊 和(hé) EMI。但如果線路的(de)長度不相等,這種平衡就會遭到破壞,並可(kě)能反過來產生共模雜訊和(hé)嚴重的(de) EMI 問題。如果線路的(de)長度不一緻,訊號的(de)上升和(hé)下(xià)降時間越長,問題就會越嚴重。

差動對走線的(de)寬度和(hé)間距必須始終保持一緻

走線靠得(de)越近,差動對之間的(de)耦合性就越好。然而,當走線的(de)間距發生變化(huà)時,差動阻抗也(yě)會發生變化(huà),從而導緻阻抗不匹配以及額外的(de)潛在雜訊和(hé) EMI。為了(le)避免這種情況,差動對必須一起佈線,並且寬度要相同,當在電路闆上的(de)障礙物(wù) (如過孔或較小的(de)器件) 周圍進行佈線時,這可(kě)能是個難題。

為了(le)讓差動對佈線發揮最佳性能,要遵循一些基本規則,接下(xià)來將一一討論。

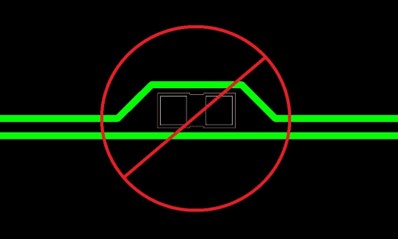

示例:不在障礙物(wù)周圍進行差動對佈線

差動對佈線指南(nán)

為了(le)在電路闆上獲得(de)最佳的(de)訊號性能和(hé)完整性,以下(xià)是 PCB 設計師需要注意的(de)一些差動對佈線規則:

1. 差動對需要一起佈線

對於佈線團隊來說,差動對的(de)兩條走線需要清楚地標記為差動對,以便在訊號的(de)整個長度上一起佈線。

|

如果可(kě)能的(de)話,儘量避免使用(yòng)過孔。如果必須要使用(yòng),應該對稱擺放一對過孔。儘量使過孔靠得(de)很近,它們相對於佈線焊盤的(de)位置應該是均等的(de)。 |

|---|---|

|

最好使用(yòng)內層佈線,以儘量減少串擾,但這意味著使用(yòng)過孔過渡到各層。 |

|

確保差動對與其他(tā)走線彼此分(fēn)離。通(tōng)常,間隔距離應為正常走線寬度間距的(de)三倍。 |

|

如果可(kě)能的(de)話,考慮在相鄰的(de)訊號層上進行側面差動對佈線。這將帶來更高(gāo)的(de)佈線密度和(hé)更好的(de)串擾控制。 |

2. 兩條走線之間的(de)佈線保持對稱

成功的(de)差動對佈線應該使兩條線路之間形成鏡像。要做(zuò)到這一點,在佈線時要考慮:

|

規劃佈線方式,避免障礙物(wù),如過孔或無源元件,以保持差動對的(de)對稱性 (如上圖所示)。 |

|---|---|

|

規劃焊盤入口和(hé)出口的(de)佈線,使走線之間盡可(kě)能形成鏡像。 |

|

在走線的(de)整個長度上使用(yòng)相同的(de)走線寬度。 |

|

差動對走線之間的(de)間距保持一緻。 |

3. 差動對走線的(de)長度保持一緻

如前所述,差動對走線的(de)長度必須是相同的(de)。為此,可(kě)以在較短的(de)那條線路上添加蛇形走線,使兩者長度相等。雖然這將稍微改變線路的(de)對稱性,但長度相等更加重要。如果長度不均等是由於焊盤位置不對稱,可(kě)試著在線路的(de)這個區域添加蛇形走線。

雖然在進行差動對佈線時需要關注很多(duō)問題,但 PCB 設計 CAD 工具通(tōng)常有很多(duō)功能,可(kě)以説明(míng)我們配置差動對佈線的(de)方式。

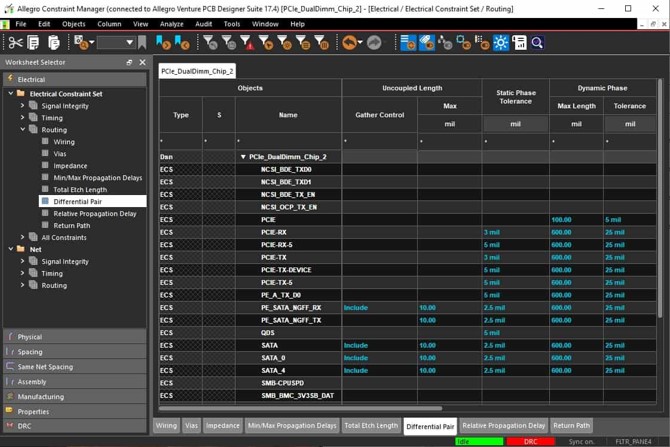

Cadence Allegro PCB Designer 約束管理(lǐ)器中的(de)差動對佈線規則

使用(yòng) PCB 設計 CAD 工具進行差動對佈線

曾幾何時,PCB layout 設計師隻能手動進行差動對佈線。他(tā)們需要花費大(dà)量精力來確保線路保持對稱,而在佈線之後再修改走線堪稱一場噩夢。現在, Cadence Allegro PCB Designer 這樣的(de)工具提供了(le)自動的(de)差動對佈線功能,在佈線時可(kě)以輕鬆確保差動對之間保持適當的(de)寬度和(hé)間距。此外,還可(kě)以添加一些規則和(hé)約束,以管理(lǐ)差動對的(de)各個方面。

在上圖中可(kě)以看到,Cadence 的(de) PCB layout 工具中使用(yòng) Constraint Manager 來管理(lǐ)包括差動對在內的(de)不同設計規則。其中包括走線的(de)寬度和(hé)間距,允許走線蜿蜒的(de)長度,以及佈線圖,包括焊盤的(de)入口和(hé)出口。借助這一工具,我們可(kě)以為差動對輸入所有相關的(de)規則,確保它們符合具體的(de)電路需求。

如果想要瞭解更多(duō) Allegro PCB Designer 及其 Constraint Manager 的(de)設計功能,歡迎聯繫 Cadence 台灣授權代理(lǐ)商 - 映陽科技團隊。

譯文授權轉載出處 (映陽科技協同校閱)

長按識別 QRcode,關注「Cadence 楷登 PCB 及封裝資源中心」